|

||||

|

|

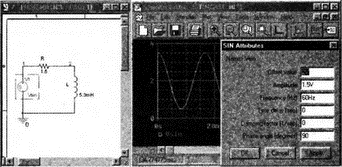

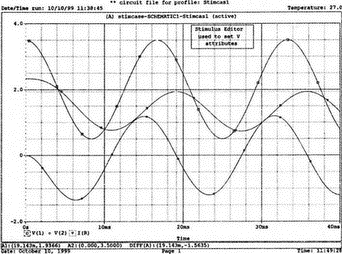

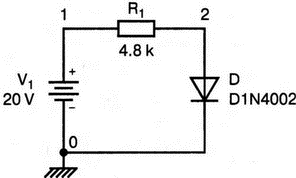

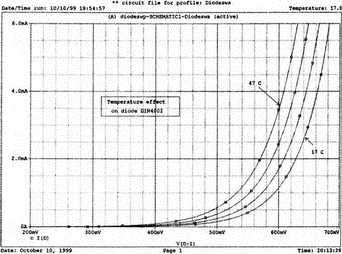

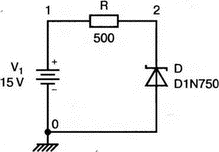

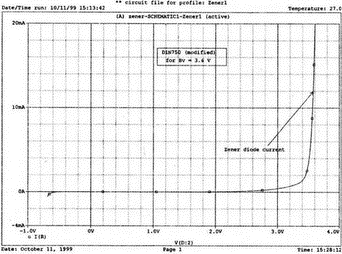

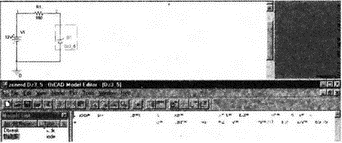

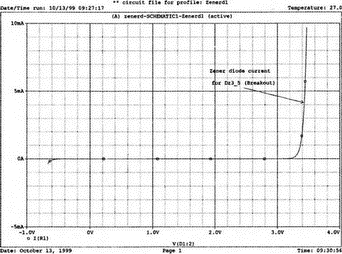

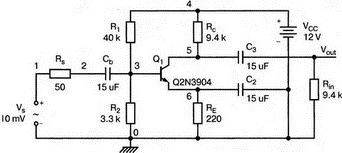

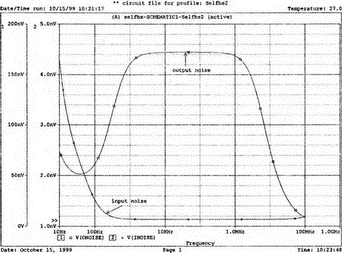

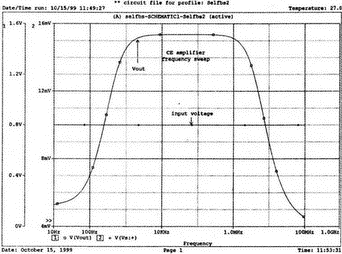

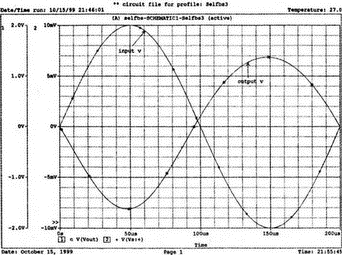

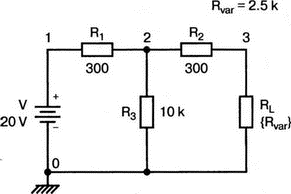

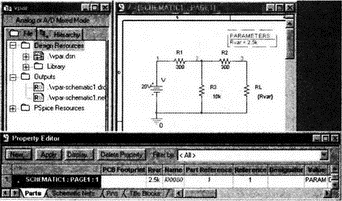

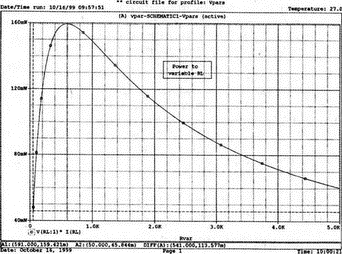

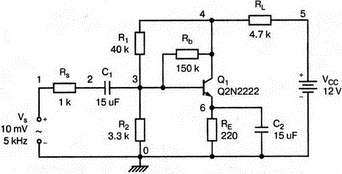

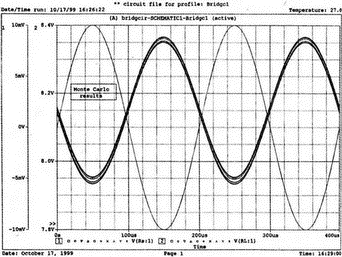

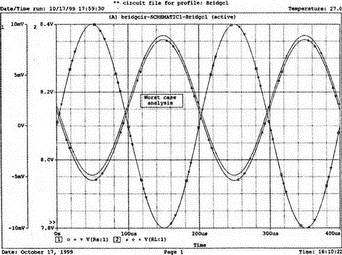

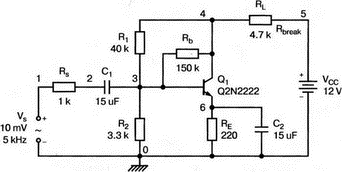

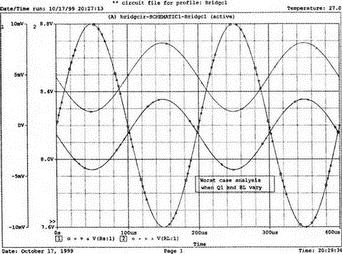

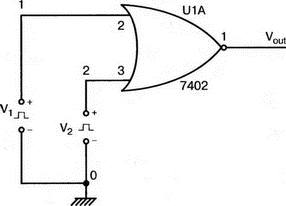

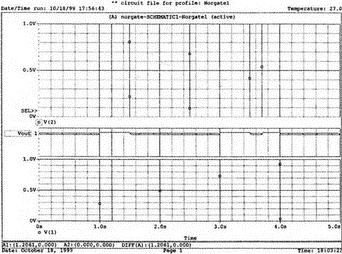

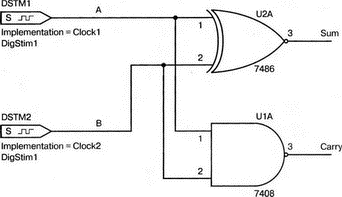

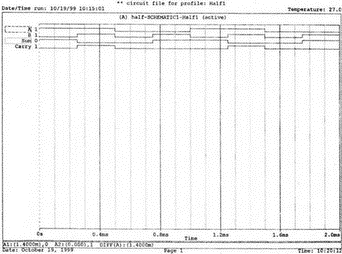

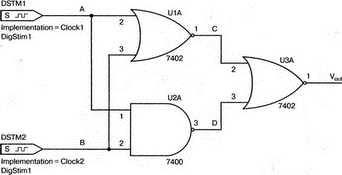

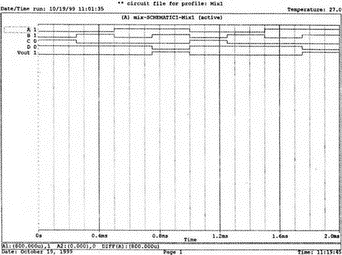

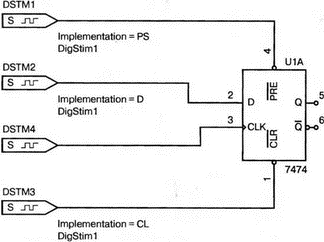

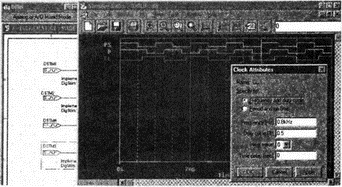

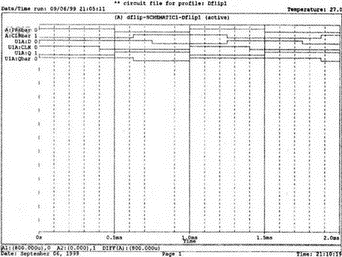

17. Другие темы в CaptureПользователю PSpice и Capture могут быть интересны и другие темы. Некоторые из них, однако, чаще используются в коммерческой версии Capture, например, редактор Stimulus. Редактор StimulusВ PSpice используются различные формы (stimuli) напряжений или токов. Формы напряжения, представляемые синусоидой, экспонентой, прямоугольными импульсами, кусочно-линейной функцией (PWL), квазигармоникой с модулируемой частотой, рассматривались в последнем разделе главы 4. Для краткого знакомства с методикой применения редактора Stimulus в Capture, рассмотрим источник синусоидального напряжения, который имеет эту форму sin(<vo> <va> <f> <td> <df> <phase>), где vo — напряжение смещения, va — амплитуда напряжения, f — частота, td — запаздывание, df — коэффициент затухания и phase — начальная фаза синусоидального сигнала. В PSpice команда ввода выглядит как V 1 0 sin (0.3V 1V 500Hz 0 500 0) Эта команда использовалась в примере главы 4 (см. полученный в результате график на рис. 4.30). С другой стороны, синусоидальный источник тока можно было бы ввести как I 1 0 sin(0.2А 0.75А 60Hz 0 0 90) Здесь первый параметр io — ток смещения, второй параметр ia — амплитуда тока, а остальные параметры не отличаются от приведенных в команде для источника напряжения. Редактор Stimulus программы Capture разрешает пользователю просмотреть график заданного сигнала на экране до того, как он будет использован в схеме. Это справедливо для всех форм напряжения, которые поддерживаются OrCAD PSpice. Однако редактор Stimulus демонстрационной версии можно использовать только для функции sin(). В качестве простого примера начнем новый проект с именем stimcase и вызовем компонент VSTIM из библиотеки SOURCSTM для формирования синусоидального напряжения. Вставьте в схему последовательную цепочку из R=1,5 Ом и L=5,3 мГн, как на рис. 2.1. Выберите свойства реализации источника напряжения (implementation) и назовите его Vsin. Затем выберите символ для формы и из главного меню выберите Edit, PSpice Stimulus. Появится окно Stimulus Editor. Если вы используете демонстрационную версию, то сможете устанавливать в этом окне атрибуты только для синусоидальной формы. Окно для установки атрибутов SIN() показано на рис. 17.1 и должно быть заполнено так, как в приведенном примере. Установите следующие значения: Offset value=2 В, Amplitude=1,5 В, Frequency(Hz)= 0 Гц, Time delay(с)=0, Damping factor(1/c)=0 и Phase angle(градусы)=90. После установки значений в окне предварительного просмотра появится диаграмма синусоидального напряжения. Оно должно иметь максимальное значение 3,5 В и минимальное 0,5 В, создавая значение двойной амплитуды 3 В (или амплитуду 1,5 В), постоянную составляющую, равную 2 В, и начальный фазовый угол 90°.  Рис. 17.1. Окно для установки атрибутов синусоидального сигнала Когда вы нажмете OK, закрывая окно SIN Attribute, появится запрос, хотите ли вы сохранить изменения (ответьте «да») и модифицировать схемное решение (ответьте «да»). Подготовьте моделирование на PSpice, выбрав New Simulation Profile с именем Stimcas1 и выберите анализ переходных процессов во временной области для интервала в 40 мс с максимальным размером шага 40 мкс. Проведите моделирование и получите в Probe графики V(1), V(2) и I(R) на одном экране, как показано на рис. 17.2. В начале графика входное напряжение имеет значение 3,5 В, как и при предварительном просмотре формы. Другие кривые искажены из-за переходного процесса. Выберите момент, когда V(1) находится в максимуме при t=16,68 мс, затем найдите момент, когда в максимуме находится ток при t=19,143 мс. Отметьте, что ток отстает от приложенного напряжения на 2,463 мс, что соответствует 53,1°. Результаты не отличаются от полученных в соответствующем примере из главы 2.  Рис. 17.2. Временные диаграммы, полученные с использованием Stimulus Editor В качестве упражнения убедитесь, что ток имеет величину 0,6015 А, а напряжение на катушке индуктивности равно 1,1933 В. Отметим, что в представленном примере величина входного напряжения составляет 1,5 В, в то время как в первом примере из главы 2 оно было равно 1,0 В. **** 10/10/99 11:38:45 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Stimcas1 **** CIRCUIT DESCRIPTION *Libraries: * Local Libraries : .STMLIB ".\STIMCASE.stl" * From [PSPICE NETLIST] section of pspieeev.ini file: .lib nom.lib *Analysis directives: .TRAN 0 40ms 0 40us .PROBE *Netlist File: .INC "stimcase-SCHEMATIC1.net" * Alias File: **** INCLUDING stimcase-SCHEMATIC1.net **** * source STIMCASE L_L 2 0 5.3mH R_R 1 2 1.5 V_V1 1 0 STIMULUS=Vsin **** RESUMING stimcase-SCHEMATIC1-Stimcas1.sim.cir **** .INC "stimcase-SCHEMATIC1.als" **** INCUDING stimcase-SCHEMATIC1.als **** .ALIASES L_L L(1=2 2=0 ) R_R R(1=1 2=2 ) V_V1 V1(+=1 -=0 ) .ENDALIASES **** RESUMING stimcase-SCHEMATIC1-Stimcas1.sim.cir **** .END * E:\SPICE\STIMCASE.stl written on Sun Oct 10 11:02:54 1999 * by Stimulus Editor -- Evaluation Version 9.0 ;!Stimulus Get ;! Vsin Analog ;!Ok ;!Plot Axis_Settings ;!Xrange 0s 60ms ;!Yrange 0 4 ;!AutoUniverse ;!XminRes 1ns ;!YminRes 1n ;!Ok .STIMULUS Vsin SIN( 2V 1,5V 60Hz 0 0 90 ) **** INITIAL TRANSIENT SOLUTION TEMPERATURE = 27.000 DEG С NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 3.5000 ( 2) 0.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT V_V1 -2.333E+00 TOTAL POWER DISSIPATION 8.17Е+00 WATTS Рис. 17.3. Выходной файл для анализа с использованием Stimulus Editor Выходной файл показан на рис. 17.3. Форма напряжения представляет собой синусоидальную зависимость (сдвинутую на 2 В по оси Y) V_V1 1 0 STIMULUS=Vsin .STIMULUS Vsin SIN( 2V 1.5V 60Hz 0 0 90 ) Выходной файл включает также ссылку на новую библиотеку STIMCASE.stl, созданную при использовании редактора Stimulus. Содержание этой библиотеки показано в выходном файле перед выводом решения для переходного процесса. Мы заключаем, что проще использовать различные формы токов и напряжений в PSpice (как в главе 4), чем пытаться использовать единственную форму, доступную в Capture. В PSpice вышеупомянутая команда просто заменяется на V 1 0 sin(2V 1.5V 60Hz 0 0 90) Если вам необходимо применить источник тока или напряжения типов ехр(), pulse(), pwl(), sffm() или sin(), используйте методы, описанные в первых тринадцати главах этой книги. Характеристики при вариации по температуреСоздайте в Capture новый проект с именем diodeswp и введите схему, показанную на рис. 17.4. Значения следующие: V1=20 В, R1=4,8 Ом, для компонента D (из библиотеки eval) выбран тип D1N4002. Цель этого анализа состоит в том, чтобы показать влияние температуры на вольт-амперную характеристику диода. Сохраните схему и подготовьте новую конфигурацию моделирования на PSpice с именем diodesws. Тип анализа — вариация для постоянных составляющих и Primary Sweep для источника постоянного напряжения V1.  Рис. 17.4. Схема с диодом для проведения вариации по температуре Установите вариацию от 0 до 30 В с шагом в 0,1 В. Нажмите кнопку «Apply», затем выберите поле Secondary Sweep и маркер температуры. Тип вариации линейный, от 17 до 47° с шагом 10°. Температура измеряется в градусах Цельсия. Выбранные значения показаны на рис. 17.5.  Рис. 17.5. Установки моделирования для температурной вариации (temperature sweep) Проведите моделирование и, представив в Probe напряжение V(D:1) по оси X, получите затем график I(D). Будет выведено семейство из четырех кривых. Крайняя левая кривая соответствует самой высокой температуре, в то время как крайняя правая — самой низкой. Промаркируйте их соответственно. Сравните ваши результаты с графиками на рис. 17.6.  Рис. 17.6. Влияние температуры на характеристики диода D1N4002 **** 10/10/99 19:54:57 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profiles Diodesws *Libraries: * Local Libraries : * From [PSPICE NЕТLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .DC LIN V_V1 0V 30V 0.1V + LIN TEMP 17 47 10 .PROBE *Netlist File: .INC "diodeswp-SCHEMATIC1.net" * Alias File: **** INCLUDING diodeswp-SCHEMATIC1.net **** * source DIODESWP D_D 2 0 D1N4002 R_R1 1 2 4.8k V_V1 1 0 20V **** RESUMING diodeswp-SCHEMATIC1-Diodesws.sim.cir **** .INC "diodeswp-SCHEMATIC1.als" **** INCLUDING diodeswp-SCHEMATIC1.als **** .ALIASES D_D D(1=2 2=0 ) R_R1 R1(1=1 2=2 ) V_V1 V1(+=1 -=0 ) _ _(1=1) _ _(2=2) .ENDALIASES **** RESUMING diodeswp-SCHEMATIC1-Diodesws.sim.cir **** .END ** circuit file for profile: Diodesws **** Diode MODEL PARAMETERS D1N4002 IS 14.110000Е-09 N 1.984 ISP 100.000000E-12 IKF 94.81 BV 100.1 IBV 10 RS .03389 TT 4.761000E-06 CJO 51.170000E-12 VJ .3905 M .2762 Рис. 17.7. Выходной файл вариации по температуре В выходном файле (рис. 17.7) показана директива анализа .DC LIN V_V1 0V 3 0V 0.1V + LIN TEMP 17 47 10 но отсутствует информация о рабочей точке, и мы заключаем, что этот тип задач в PSpice обрабатывается лучше, чем в Capture. В PSpice достаточно было бы просто поместить директиву .ОР во входном файле, чтобы получить в выходном файле значения рабочей точки. Изменение напряжения зенеровского пробояПоскольку в демонстрационной версии PSpice доступен лишь один тип зенеровского диода — D1N750, вам необходимо будет изменять напряжение пробоя, чтобы ввести в схему диод другого типа. Начните в Capture новый проект с именем zener. Введите схему, показанную на рис. 17.8, с источником постоянного тока V1=12 В, R=500 Ом и диодом D1N750 из библиотеки eval. Закончив рисунок, выберите диод и из пункта Edit на главном меню выберите PSpice Model. При этом откроется окно OrCAD Model Editor, в котором появится список с описанием свойств диода. Каждой строке описания предшествует звездочка (*). Предположим, что для нашей схемы необходим диод с напряжением пробоя Bv=3,6 В. Переместите курсор на поле этого параметра на правой панели окна и замените значение 4,7 значением 3,6. Сохраните изменение, затем выйдите из Model Editor. Изменение, которое мы сделали, относится только к этому проекту и создаст новую библиотеку zener.lib в вашем каталоге Spice.  Рис. 17.8. Схема с зенеровским диодом Сохраните схему и выберите PSpice, New Simulation Profile с именем Zener1. Выполните вариацию для постоянного тока по входному напряжению V1 от -1 до 15 В с шагом 0,01 В. При этом вы получите информацию для построения характеристики диода. Проведите моделирование и в Probe замените ось X для графика на V(D:2). По этой оси будет откладываться напряжение между узлом 2 и «землей». Получите график I(R). Ток в контуре направлен по часовой стрелке. Возникающий в результате график показан на рис. 17.9. Как видно из него, напряжение пробоя для диода приблизительно равно 3,6 В.  Рис. 17.9. Схема изменения характеристик зенеровского диода **** 10/11/99 15:13:42 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Zener1 *Libraries: * Local Libraries : .LIB ".\zener.lib" * From [PSPICE NETLIST] section of pspiceev.ini files .lib nom.lib *Analysis directives: .DC LIN V_V1 -1V 15V 0.01V .PROBE *Netlist File: .INC "zener-SCHEMATIC1.net" *Alias File: **** including zener-SCHEMATIC1.net **** * source ZENER R_R 1 2 500 V_V1 1 0 15V D_D 0 2 D1N750 **** RESUMING zener-SCHEMATIC1-Zener1.sim.cir **** .INC "zener-SCHEMATIC1.als" **** INCLUDING zener-SCHEMATIC1.als **** .ALIASES R_R R(1=1 2=2 ) V_V1 V1(+=1 -=0 ) D_D D(1=0 2=2 ) _ _(1=1) _ _(2=2) .ENDALIASES **** RESUMING zener-SCHEMATIC1-Zener1.sim.cir **** .END ** circuit file for profile: Zener1 **** Diode MODEL PARAMETERS D1N750 IS 880.500000E-18 ISR 1.859000E-09 BV 3.6 IBV .020245 NBV 1.6989 IBVL 1.955600E-03 NBVL 14.976 RS .25 CJO 175.000000E-12 VJ .75 M .5516 TBV1 -21.277000E-06 Рис. 17.10. Характеристика зенеровского диода с напряжением пробоя 3,6 В Рассматривая выходной файл (рис. 17.10), отметим, что напряжение пробоя равно 3,6 В в соответствии с внесенным нами изменением. Имеется также директива .LIB ".\zener.lib" Она ссылается на новую локальную библиотеку, используемую в этом проекте. Листинг для диода: D_D 0 2 D1N750 D_D D(1=0 2=2) Идентифицируйте первый и второй полюсы. Первый полюс диода — анод (узел 0), второй полюс — катод (узел 2). Вспомним, что на графике по оси X отложено напряжение на узле 2 относительно земли V(D:2). Ток на оси Y графика выведен как положительный и представляет собой ток при обратном смещении. Теперь можно получить решение для более сложной схемы, чем приведенная схема с зенеровским диодом при Bv=3,6 В. Например, для моделирования симметричного ограничителя на базе лавинных диодов (рис. 9.14), вы можете вернуться к проекту zener, добавить необходимые и удалить все лишние компоненты и затем провести анализ, аналогичный рассмотренному выше. Другой способ изменения напряжения пробоя зенеровских диодовВ предыдущем примере использовался диод D1N750 с измененным напряжением пробоя. Программа Capture предлагает другие средства изменения параметров компонентов с помощью библиотеки breakout. Чтобы иллюстрировать это свойство, начните новый проект с именем zenerd. Схема будет содержать источник постоянного напряжения V1=12 В, R=880 Ом и новый компонент из библиотеки breakout.olb, который вы должны сделать доступным, добавив эту библиотеку в ваш проект. Выберите компонент DbreakZ, который является моделью зенеровского диода, поместите его в соответствующее место схемы и выберите Edit, PSpice Model. Появится окно OrCAD Model Editor, и на левой панели Model Name вы увидите имя модели Dbreak. Введите под ним новое имя модели: Dz3_5. В правой панели окна вы увидите . model Dbreak D Is=1e-14 Cjo=.1pf Rs=.1 Замените эту строку следующей записью: .model Dz3_5 D (Is=800.5E-18 Rs=.25 Ikf=0 N=1 Xti=3 Eg=1.11 Сjo=175p +M=.5 516 Vj=.75 Fc=.5 Isr=1.859n Nr=2 Bv=3.5 Ibv=20.245m +Nbv=1.6989) Новая модель breakout показана на рис. 17.11 вместе со схемой. В окне Model Editor выберите File, Save. Обратите внимание, что имя диода на рисунке также заменено на Dz3_5. Подготовьте моделирование на PSpice с именем Zenerd1, затем предусмотрите линейную вариацию по V1 от -1 до 12 В с шагом в 0,05 В.  Рис. 17.11. Модель для зенеровского диода с параметрами, изменяемыми по прерыванию в процессе моделирования (breakout model) Выполните моделирование и задайте по оси X переменную V(D1:2). Получите график I(R1). Сравните его с графиком на рис. 17.12, на котором напряжение зенеровского пробоя равно 3,5 В. В выходном файле на рис. 17.13 показаны параметры модели диода, идентифицированного как Dz3_5.  Рис. 17.12. Характеристика зенеровского диода при Bv = 3,5 В **** 10/13/99 09:27:17 *********** Evaluation PSpice (Nov 1998) *************** ** circuit file for profile: Zenerd1 *Libraries: * Local Libraries : .LIB ".\zenerd- lib" * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib * Analysis directives: .DC LIN V_V1 -1V 12V 0.05V .PROBE *Netlist File: .INC "zenerd-SCHEMATIC1.net" *Alias File: **** INCLUDING zenerd-SCHEMATIC1.net **** * source ZENERD D_D1 0 2 Dz3_5 R_R1 1 2 880 V_V1 l 0 12V **** RESUMING zenerd-schematic1-zenerd1.sim.cir **** .INC "zenerd-SCHEMATIC1.als" **** INCLUDING zenerd-SCHEMATIC1.als **** .ALIASES D_D1 D1(1=0 2=2 ) R_R1 R1(1=1 2=2 ) V_V1 V1(+=1 -=0 ) .ENDALIASES **** RESUMING zenerd-schematic1-zenerd1.sim.cir **** .END WARNING -- Library file E:\SPICE\zenerd.lib has changed since index file zenerd.ind was created. WARNING — The timestamp changed from Wed Oct 13 09:24.441999 to Wed Oct 13 09:27:04 1999. Making new index file zenerd.ind for library file zenerd.lib Index has 2 entries from 1 file(s). ** circuit file for profile: Zenerd1 **** Diode MODEL PARAMETERS Dz3_5 IS 800.500000Е-18 ISR 1.859000E-09 BV 3.5 IBV .020245 NBV 1.6989 RS .25 СJO 175.000000E-12 VJ .75 M .5516 Рис. 17.13. Выходной файл для зенеровского диода при Bv = 3,5 В Анализ шумаВ типичной схеме переменного тока шум вызывается хаотическим движением молекул в резисторах, диодах и транзисторах. Это свойство заложено в модели резисторов и полупроводниковых компонентов, используемых в PSpice. В качестве примера создадим в Capture новый проект с именем selfbs. Введите схему, показанную на рис. 17.14. Используйте компонент типа VAC для источника величиной 10 мВ и компонент Q2N3904 для транзистора. При выборе транзистора измените его коэффициент усиления, задав hFE=100, для чего, выбрав из главного меню Edit, PSpice Model, измените значение Bf на 100.  Рис. 17.14. Транзисторный усилитель, для которого проводится анализ шума Подготовьте моделирование на PSpice с именем selfbs1. Установите для анализа шума (ас sweep/noise) логарифмическую вариацию от 10 Гц до 100 МГц (в PSpice записывается 100MegHz) с шагом 20 точек на декаду. Проверьте поле Noise Analysis Enabled. Псевдоним выходного узла Vout должен быть введен как «V(Vout)», а входным узлом для схемы будет выход источника переменного напряжения Vs. Используйте интервал 100 и щелкните OK. Проведите моделирование на PSpice и получите график V(ONOISE), затем добавьте ось Y и получите график V(INOISE). Сравните ваши результаты с показанными на рис. 17.15. Обратите внимание, что в полезном диапазоне работы схемы, вблизи от нашей типовой частоты 5 кГц, шум на выходе равен 171,6 нВ, в то время как шум на входе составляет 1,136 нВ. Последнее значение не является шумом самого источника Vs, но представляет собой усиленный бесшумной схемой шум от эквивалентного источника, включенного на входе. Шум эквивалентного источника учитывает суммарный эффект от шума всех компонентов схемы и частотную характеристику усилителя.  Рис. 17.15. Результаты анализа шума для транзисторного усилителя Чтобы увидеть влияние последнего фактора, желательно снять и саму частотную характеристику. Для этого можно получить графики входного и выходного напряжений. Они могут быть получены аналогично. Получите эти графики в выбранном диапазоне частот, использовав на сой раз V(Vout) и (V Vs:+). Как показано на рис. 17.16, при типичной рабочей частоте в 5 кГц величина выходного напряжения равна 1,51 В при величине входного напряжения в 10 мВ. Можно также видеть, что выходное напряжение падает при низких и высоких частотах.  Рис. 17.16. Частотная характеристика усилителя ОЭ На рис. 17.17 показаны только перечень компонентов, псевдонимы и параметры смещения. Остальная часть выходного файла показана на рис. 17.18. Анализ шума сведен в таблицы только для f=10 Гц и f=1 МГц. Это определяется установкой интервала «100» в анализе шума. Если бы вместо этого было установлено значение «10», то таблица анализа шума включала бы частоты, равные 10,316 Гц, 1,316 кГц и так далее, создав 36 страниц в выходном файле. Если значение интервала установить равным 20, таблица анализа шума будет включать следующие частоты: 10, 100 Гц, 1, 10 кГц и далее соответственно. **** 09/04/99 20:29:50 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Selfbs1 *Libraries: * Local Libraries : .LIB ".\selfbs.lib" * From [PSPICE NETLIST] section of pspiceev.ini files .lib nom.lib *Analysis directives: .AC DEC 20 10Hz 100MegHz .NOISE V([VOUT]) V_VS 100 * PROBE *Netlist File: .INC "selfbs-SCHEMATIC1.net" * Alias File: **** INCLUDING selfbs-SCHEMATIC1.net **** * source SELFBS R_Rin VOUT 0 9.4k R_RE 6 0 220 R_RC 4 5 9.4k R_R2 3 0 3.3k R_R1 4 3 40k R_Rs 1 2 50 V_Vs 1 0 DC 0V AC 10mV Q_Q1 5 3 6 Q2N3904 C_C2 6 0 15uF C_C3 5 VOUT 15uF C_Cb 2 3 15uF V_VCC 4 0 12V **** RESUMING selfbs-SCHEMATIC1-Selfbs1.sim.cir **** .INC "selfbs-SCHEMATIC1.als" **** INCLUDING selfbs-SCHEMATIC1.als **** .ALIASES R_Rin Rin(1=VOUT 2=0 ) R_RE RE(1=6 2=0 ) R_RC RC(1=4 2=5 ) R_R2 R2(1=3 2=0 ) R_R1 R1(1=4 2=3 ) R_Rs Rs(1=1 2=2 ) V_Vs Vs(+=1 -=0 ) Q_Q1 Q1(c=5 b=3 e=6 ) С_C2 C2(1=6 2=0 ) C_C3 C3(1=5 2=VOUT ) С_Cb Cb(1=2 2=3 ) V_VCC VCC(+=4 -=0 ) .ENDALIASES **** RESUMING selfbs-SCHEMATIC1-Selfbs1.sim.cir **** .END **** BJT MODEL PARAMETERS Q2N3904 NPN IS 6.734000E-15 BF 100 **** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .8722 ( 4) 12.0000 ( 5) 3.2056 ( 6) .2089 ( VOUT) 0.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT V_Vs 0.000E+00 V_VCC -1.214E-03 TOTAL POWER DISSIPATION 1.46E-02 WATTS Рис. 17.17. Часть выходного файла для анализа шума, показывающая перечень элементов, псевдонимы и параметры смещения ** circuit file for profile: Selfbs1 NOISE ANALYSIS TEMPERATURE = 27.000 DEG С FREQUENCY = 1.000E+01 HZ **** TRANSISTOR SQUARED NOISE VOLTAGES (SQ V/HZ) Q_Q1 RB 5.570E-17 RC 1.250E-24 RE 0.000E+00 IBSN 1.900E-15 IС 1.505E-16 IBFN 0.000E+00 TOTAL 2.107E-15 **** RESISTOR SQUARED NOISE VOLTAGES (SQ V/HZ) R_Rin R_RE R_RC R_R2 R_R1 R_Rs TOTAL 3.865E-17 1.176E-15 3.817E-17 1.650Е-15 1.361E-16 2.413E-16 **** TOTAL OUTPUT NOISE VOLTAGE = 5.387E-15 SQ V/HZ = 7.339E-08 V/RT HZ TRANSFER FUNCTION VALUE: V(VOUT)/V_Vs = 1.706E+01 EQUIVALENT INPUT NOISE AT V Vs = 4.301E-09 V/RT HZ FREQUENCY = 1.000E+06 HZ **** TRANSISTOR SQUARED NOISE VOLTAGES (SQ V/HZ) Q_Q1 RB 3.773E-15 RC 6.86CE-22 RE 0.000E+00 IBSN 3.552Е-16 IС 5.682E-15 IBFN 0.000E+00 TOTAL 9.810E-15 **** RESISTOR SQUARED NOISE VOLTAGES (SQ V/HZ) R_Rin R_RE R_RC R_R2 R_R1 R_Rs TOTAL 3.342Е-17 1.932E-22 3.342E-17 2.767E-16 2.283E-17 1.826E-14 **** TOTAL OUTPUT NOISE VOLTAGE = 2.844E-14 SQ V/HZ = 1.686E-07 V/RT HZ TRANSFER FUNCTION VALUE: V(VOUT)/V_Vs = 1.484E+02 EQUIVALENT INPUT NOISE AT V_Vs = 1.136E-09 V/RT HZ Рис. 17.18. Часть выходного файла анализа шума, показывающая результаты анализа шума Трудно оценить результаты шумового анализа на простой схеме. Если не имеется многокаскадных или других схем, которые будут использоваться для сравнения, полученные для шумовых напряжений значения будут сомнительны. Обратите внимание, что спектральные плотности шума как транзистора, так и резистора, приведены для каждой выбранной частоты. Листинг содержит также общее напряжение шума на выходе, обозначенное как передаточная функция Vout/Vs. В знаменателе показан упомянутый ранее входной шум эквивалентного источника. В качестве упражнения проведите анализ снова, задав интервал «10» при анализе шума, затем загрузите выходной файл selfbsI.out з программу текстового редактора. Распечатайте только сведенные в таблицу результаты для f=10 кГц, и сравните ваши результаты с показанными на рис. 17.19. При типичней рабочей частоте сравните шумовые уровни напряжения транзистора и резисторов с показанными для f=10 Гц и f=1 МГц на рис. 17.18. Также обратите внимание, что отношение Vout/Vs=151,4 не отличается от результата, полученного в Probe. ** circuit file for profile: Selfbs1 *Analysis directives: .AC DEC 20 10Hz 100MegHz .NOISE V([VOUT]) V_Vs 20 .PROBE *Netlist File: .INC "selfbs-SCHEMATIC1.net" **** NOISE ANALYSIS TEMPERATURE = 27.000 DEG С FREQUENCY = 1.000E+04 HZ **** TRANSISTOR SQUARED NOISE VOLTAGES (SQ V/HZ) Q_Q1 RB 3.926E-15 RC 4.921E-23 RE 0.000E+00 IBSN 3.701E-16 IC 5.912E-15 IBFN 0.000E+00 TOTAL 1.021E-14 **** RESISTOR SQUARED NOISE VOLTAGES (SQ V/HZ) R_Rin R_RE R_RC R_R2 R_R1 R_Rs TOTAL 3.483E-17 2.010E-18 3.483E-17 2.880E-16 2.376E-17 1.900E-14 **** TOTAL OUTPUT NOISE VOLTAGE = 2.959E-14 SQ V/HZ = 1.720E-07 V/RT HZ TRANSFER FUNCTION VALUE: V(VOUT)/V_Vs = 1.514E+02 EQUIVALENT INPUT NOISE AT V_Vs = 1.136E-09 V/RT HZ Рис. 17.19. Выходной файл, использующий интервал «10» при анализе шума Гармонический состав выходного напряженияПродолжая изучение усилителя в проекте selfbs, сравним входное синусоидальное напряжение с синусоидальным выходным напряжением, чтобы увидеть, ограничивается ли выходное напряжение или проявляется какое-либо другое искажение его формы. Чтобы выполнять анализ, заменим источник входного напряжения типа VAC на источник типа VSIN. Зададим нулевое напряжение смещения, амплитуду в 10 мВ и частоту в 5 кГц. Подготовим моделирование на PSpice с именем Selfbs2 и выполним анализ переходных процессов на временном интервале в 0,2 мс с максимальным размером шага в 0,2 мкс. Нажмите кнопку Output File Options и выберите поле Fourier analysis. Установите основную частоту в 5 кГц и число гармоник, равное 5. Выходная переменная — V(Vout). Выполните моделирование и получите в Probe графики V(Vout) и V(Vs:+). После соответствующей маркировки кривых сравните результаты с представленными на рис. 17.20. На первый взгляд, выходное напряжение кажется точной копией входного, перевернутой на 180°. Используйте курсор, чтобы найти первый отрицательный минимум и первый положительный максимум выходного напряжения. Они равны -1,61 В и 1,372 В соответственно и отличаются из-за того, что мы рассматриваем первый период переходного процесса.  Рис. 17.20. Сравнение временных диаграмм входного и выходного напряжений В лаборатории осциллограф не отобразил бы переходные процессы, и мы увидели бы искажение в чистом виде. Это искажение характеризуется гармоническим составом и хорошо отражено в выходном файле, часть которого показана на рис. 17.21. Первая (основная) гармоника имеет частоту f=1 кГц с амплитудой 1,491 В. Сравнивая эту величину с амплитудами остальных гармоник от второй до пятой, мы видим, что влияние более высоких гармоник невелико. Если мы просто сложим величины перечисленных гармоник, то получим результат 1,61 В. В прежнем анализе, использующем источник типа VAC в качестве входного, мы нашли, что Vout=1,51 В. Значение 1,61 В, очевидно, неверно для выходного напряжения, так как мы пренебрегли фазовыми углами отдельных гармоник. Обратите внимание, что общее гармоническое искажение меньше чем 7,7%. **** 09/05/99 13:29:29 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profiles Selfbs2 * Local Libraries : .LIB ".\selfbs.lib" * From [PSPICE NETLIST] section of pspiceev.ini files .lib nom.lib *Analysis directives: .TRAN 0.02ms 0.2ms 0 0.2us .FOUR 5kHz 5 V([VOUT]) .PROBE *Netlist Files .INC "selfbs-SCHEMATIC1.net" *Alias File: **** INCLUDING selfbs-SCHEMATIC1.net **** * source SELFBS R_Rin VOUT 0 9.4k R_RE 6 0 220 R_RC 4 5 9.4k R_R2 3 0 3.3k R_R1 4 3 40k R_Rs 1 2 50 Q_Q1 5 3 6 Q2N3904 C_C2 6 0 15uF C_C3 5 VOUT 15uF С_Cb 2 3 15uF V_CC 4 0 12V V_Vs 1 0 +SIN 0 10mV 5kHz 0 0 0 .INC "selfbs-SCHEMATIC1.als" .ENDALIASES **** INITIAL TRANSIENT SOLUTION TEMPERATURE = 27.000 DEG С NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .8722 ( 4) 12.0000 ( 5) 3.2056 ( 6) .2089 ( VOUT) 0.0000 VOLTAGE SOURCE CURRENTS NAME CURRENT V_VCC -1.214E-03 V_Vs 0.000E+00 TOTAL POWER DISSIPATION 1.46E-02 WATTS **** FOURIER ANALYSIS TEMPERATURE = 27.000 DEG С FOURIER COMPONENTS OF TRANSIENT RESPONSE V(VOUT) DC COMPONENT = -8.776912E-03 HARMONIC FREQUENCY FOURIER NORMALIZED PHASE NORMALIZED NO (HZ) COMPONENT COMPONENT (DEG) PHASE (DEG) 1 5.000E+03 1.491E+00 1.000E+00 -1.760Е-02 0.000E+00 2 1.000E+04 1.146E-01 7.688E-02 9.978E+01 2.757E+02 3 1.500E+04 4.701E-03 3.1541-03 1.098E+01 1.9491+02 4 2.000E+04 2.146E-04 1.440E-04 -1.622E+00 1.743E+02 5 2.500E+04 1.567E-04 1.051E-04 -8.367E+00 1.676E+02 TOTAL HARMONIC DISTORTION = 7.694897E+00 PERCENT Рис. 17.21. Выходной файл, показывающий гармонический состав от первой до пятой гармоники Использование изменяемого параметраНачните новый проект vpar и введите компоненты для схемы, показанной на рис. 17.22. Значения параметров следующие: V=20 В, R1=300 Ом, R2=300 Ом, R3=10 кОм, RL=2,5 кОм. Значение для RL показано на рисунке не так, как оно показывается при вариации на постоянном токе (dc sweep). Закончив схему, щелкните дважды на условном обозначении RL, затем измените тип компонента на {Rvar}. Фигурные скобки используются, чтобы отразить, что значение непостоянно (имя Rvar может быть и другим по вашему выбору).  Рис. 17.22. Схема для проведения вариации по параметрам Из специальной библиотеки выбирают компонент param и вставляют его в схему в удобном месте. Двойной щелчок на символе (PARAMETERS:) выводит на экран окно Property Editor. Выберите кнопку New… В поле Property Name введите имя Rvar, затем нажмите OK. При возврате в окно Property Editor вы увидите теперь столбец с заголовком Rvar. Введите значение 2,5k и обратите внимание, что в столбце Value записано значение «PARAM», как показано на рис. 17.23. Сохраните схему и подготовьте анализ PSpice с именем Vpars. Выберите DC Sweep, нажав на маркер Linear sweep, задайте начальное значение частоты в 50 Гц и конечное в 5000 Гц с шагом в 1 Гц. Выполните моделирование и получите в Probe график произведения V(RL:1)·(RL), который является графиком мощности, выделяемой на RL (рис. 17.24). Рассчитайте по формулам стандартного схемотехнического анализа максимальную мощность, которая могла бы выделяться при переменном значении RL. Сравните ваши результаты со значением на табло курсора Рmax=159,421 мВт (рис. 17.24). В выходном файле обратите внимание на директиву для параметра Rvar: .DC LIN PARAM Rvar 50 5000 1 показывающую, что Rvar принимает последовательные целочисленные значения, начиная от 50 Ом до 5 кОм.  Рис. 17.23. Установка переменного параметра в окне Property Editor  Рис. 17.24. Зависимость мощности от параметра RL, снятая в режиме с переменным параметром Использование допусков приборовНачните в Capture новый проект с именем bridgcir. Затем введите схему, показанную на рис. 17.25. В схеме используется транзистор типа Q2N2222. В качестве входного напряжения выбран компонент VSIN с амплитудой 10 мВ и частотой f=5 кГц. Используйте значения, показанные на рисунке для резисторов, конденсаторов и источника питания постоянного тока. Установите величину допуска на параметр hFE транзистора равной ±25% следующим образом. Выберите транзистор Q1, затем из главного меню выберите Edit, PSpice Model, чтобы войти в OrCAD Model Editor.  Рис. 17.25. Схема для исследования влияния допусков транзистора на выходное напряжение На правой панели, сразу после «Bf=255,9», напечатайте «Dev=25%». Этот допуск будет относиться к параметру Вf. Затем используйте File, Save и закройте окно. После введения схемы сохраните ее. Анализ по методу Монте-КарлоДля подготовки к анализу выберем PSpice, New Simulation Profile с именем Bridgc1. Выберите Time Domain в качестве типа анализа, установите интервал моделирования в 400 мкс с максимальным шагом 0,4 мкс. Проверьте поле для Monte Carlo/Worst Case, используя выходную переменную V(RL:1). Установите число проходов равным 10 при однородном распределении и сохранении данных для всех проходов. Проведите моделирование и получите в Probe графики V(Rs:1) и V(RL:1), как показано на рис. 17.26. Затем в поле Tools Options главного меню выберите опцию Probe «never use symbols» (никогда не использовать символы), чтобы избежать перекрытия графиков символами.  Рис. 17.26. Результаты исследования влияния погрешности hFE транзистора методом Монте-Карло Обратите внимание, что некоторые графики на экране больше ожидаемых или нормальных значений, в то время как другие меньше. Это результат случайного изменения hFE в пределах допуска ±25%. Используйте курсор, чтобы найти значение каждого из вторых максимумов выходного напряжения. Они должны иметь значения 8,355, 8,365 В и так далее. На графиках, показанных здесь, минимальные и максимальные значения были 8,3501 и 8,3667 В. ** circuit file for profile: Bridgc1 *Analysis directives: .TRAN 0 400us 0 0.4us .MC 10 TRAN V(C43) VMAX OUTPUT ALL .PROBE **** INCLUDING bridgcir-SCHEMATIC1.net **** * source BRIDGCIR R_RE 6 0 220 R_R2 3 0 3.3k R_R1 4 3 40k R_RL 4 5 4.7k R_Rb 3 4 150k R_Rs 1 2 1k V_V1 1 0 +SIN 0 10mV 5kHz 0 0 0 V_VCC 5 0 12V Q_Q1 4 3 6 Q2N2222 C_C2 6 0 15uF C_C1 2 3 15uF * *** BJT MODEL PARAMETERS Q2N2222 NPN IS 14.340000E-15 BF 255.9 MONTE CARLO NOMINAL NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7593 ( 4) 8.1468 ( 5) 12.0000 ( 6) .1297 MONTE CARLO PASS 2 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7587 ( 4) 8.1580 ( 5) 12.0000 ( 6) .1293 MONTE CARLO PASS 3 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7589 ( 4) 8.1541 ( 5) 12.0000 ( 6) .1294 MONTE CARLO PASS 4 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7596 ( 4) 8.1414 ( 5) 12.0000 ( 6) .1300 MONTE CARLO PASS 10 NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7594 ( 4) 8.1460 ( 5) 12.0000 ( 6) .1298 **** SORTED DEVIATIONS OF V(4) TEMPERATURE = 27.000 DEG С MONTE CARLO SUMMARY Mean Deviation = 2.2930E-03 Sigma = 8.2363E-03 RUN MAX DEVIATION FROM NOMINAL Pass 5 .0151 (1.83 sigma) higher at T = 53.3150E-06 ( 100.19% of Nominal) Pass 2 .0128 (1.55 sigma) higher at T = 248.12001-06 ( 100,16% of Nominal) Pass 8 4.8375E-03 ( .59 sigma) lower at T = 50.9140E-06 ( 99.939% of Nominal) Pass 10 1.0772E-03 ( .13 sigma) lower at T = 246.9200E-06 ( 99.986% of Nominal) Рис. 17.27. Выходной файл с результатами анализа по методу Монте-Карло Небольшая часть выходного файла показана на рис. 17.27. Обратите внимание на две директивы, определяющие тип анализа: .TRAN 0 400us 0 0. 4us .МС 10 TRAN V([4]) YMAX OUTPUT ALL Первая директива вызывает анализ переходных процессов на интервале 400 мкс, вторая — запрашивает анализ по методу Монте-Карло с 10 проходами для отклонений напряжения V(4), которое идентично V(RL:1) на графике. Внизу выходного файла после последнего результата для анализа Монте-Карло приведен раздел, показывающий сортировку отклонений напряжения на узле 4. Данные значения представляют собой среднее и среднеквадратичное отклонение. Например, в момент t=254,24 мкс при втором проходе произошло максимальное отклонение в 100,16% от номинального значения. Анализ на наихудший случайПри предыдущем моделировании мы выполнили анализ по методу Монте- Карло, установив в окне условия в Monte Carlo/Worst Case. То же самое окно может использоваться для анализа на наихудший случай при выборе Worst Case/Sensitivity. Выходная переменная по-прежнему V(RL:1), но при выборе Worst Case/Sensitivity в поле опций необходимо выбрать «Vary devices that have only DEV tolerances» (Изменять только компоненты, которые имеют допуски DEV). Проверьте поле «Save data from each sensitivity run» (Сохранять данные прохода для каждой чувствительности) и выберите кнопку «More Settings». В следующем окне выберите «Find the maximum value (MAX)» (Находить максимальное значение) и используйте опцию «high». Проведите моделирование и получите в Probe графики V(Rs:1) и V(RL:1), как показано на рис. 17.28. Убедитесь, что уровень смещения при выводе V(RL:1) для каждого прохода составляет 8,1468, 8,1468 и 8,1603 В, максимум для 1-го и 2-го проходов равен 8,355 В, а для 3-го прохода — 8,3668 В. Значение минимума для 1-го и 2-го проходов равно 7,9391 В, а для 3-го прохода — 7,9542 В.  Рис. 17.28. Временные диаграммы при анализе на наихудший случай В итоге мы установили, что изменения параметра hFE в пределах допуска не оказывают существенного влияния на стабильность параметров усилителя. Влияние допуска резисторов на анализ наихудшего случаяВ только что проведенном анализе мы изменяли только коэффициент hFE транзистора. Каким был бы анализ на наихудший случай, при выборе резистора в качестве изменяемого фактора допуска на сопротивление? Чтобы упростить исследование, будем изменять только значение RL. Заменим представленный в схеме резистор RL компонентом «Rbreak» из библиотеки breakout. Установим сопротивление RL=4,7 кОм, как и прежде, затем выделим компонент на схеме и выберем Edit, PSpice Model. В окне OrCAD Model Editor измените запись на правой панели следующим образом: .model Rbreak RES R = 1 DEV = 20% Здесь «R=1» означает, что множитель для сопротивления равен 1; запись «DEV=20%» задает допуск в 20% на изменение сопротивления. Схема приведена на рис. 17.29. Сохраните изменения, подготовьте моделирование для анализа на наихудший случай, как в предыдущем примере. Напомним, что теперь и коэффициент усиления транзистора hFE и сопротивление RL будут изменяться в пределах допуска. Выполните моделирование и обратите внимание, что в PSpice выполняется четыре вида анализа на чувствительность: 1) номинальную, 2) по коэффициенту усиления BF транзистора Q_Q1 Q2N2222, 3) по сопротивлению R резистора R_RL Rbreak и 4) на наихудший случай, учитывающий допуски всех компонентов. Как и прежде получите в Probe графики V(Rs:1) и V(RL:1). На экране появится всего восемь графиков (рис. 17.30). Значительное отличие этого набора графиков от полученного ранее заключается в смещении графика выходного напряжения. Выбрав опцию «Use Symbol Always» (Всегда использовать символы), идентифицируйте каждую кривую по номеру прохода.  Рис. 17.29. Схема усилителя, использующая резистор из библиотеки breakout  Рис. 17.30. Результаты анализа на наихудший случай при одновременном изменении Q1 и RL Использование курсора показывает, что нижняя кривая выходного напряжения имеет постоянную составляющую в 8,1468 В. Проверьте это, измеряя размах напряжения с помощью курсора. Верхняя кривая выходного напряжения V(RL:1), связанная с модифицированной осью Y, имеет постоянную составляющую в 8,4843 В, которая может быть определена аналогичным образом. В выходном файле напряжение V(RL:1) идентифицировано как напряжение узла V(4). Оно имеет значение 8,1468 В, как для номинальной чувствительности, так и для чувствительности по коэффициенту усиления BF транзистора. Оно равно 8,4843 В для наихудшего случая, учитывающего допуски всех устройств. Часть выходного файла показана на рис. 17.31. ** circuit file for profile: Bridgc1 *Libraries: * Local Libraries : .LIB ".\bridgcir.lib" * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib * Analysis directives: .TRAN 0 400us 0 0.4us .WCASE TRAN V( [4]) MAX OUTPUT ALL VARY DEV HI .PROBE WARNING Library file e:\spice\bridgcir.lib has changed since index file bridgcir.ind was created. WARNING -- The timestamp changed from Sun Sep 05 21:51:14 1999 to Hon Sep 06 10:22:00 1999. Making new index file bridgcir.ind for library file bridgcir.lib Index has 2 entries from 1 file(s). **** BJT MODEL PARAMETERS Q2H2222 NPN IS 14.340000E-15 BF 255.9 **** Resistor MODEL PARAMETERS Rbreak R 1 SENSITIVITY NOMINAL NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7593 ( 4) 8.1468 ( 5) 12.0000 ( 6) .1297 SENSITIVITY Q_Q1 Q2N2222 BF NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7593 ( 4) 8.1468 ( 5) 12.0000 ( 6) .1297 SENSITIVITY R_RL RBREAK R NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7592 ( 4) 8.1454 ( 5) 12.0000 ( 6) .1296 SORTED DEVIATIONS OF V(4) TEMPERATURE = 27.000 DEG С SENSITIVITY SUMMARY RUN MAXIMUM VALUE NOMINAL 8.355 at T = 149.3200E-06 Q_Q1 Q2N2222 BF 8.355 at T = 149.3200E-06 ( -4.2233E-03% change per 1% change in Model Parameter) R_RL Rbreak R 8.3536 at T = 149.3200E-06 ( -.169 % change per 1% change in Model Parameter) WORST CASE ALL DEVICES DEVICE MODEL PARAMETER NEW VALUE Q_Q1 Q2N2222 BF 191.93 (Decreased) R_RL Rbreak R .8 (Decreased) NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE ( 1) 0.0000 ( 2) 0.0000 ( 3) .7870 ( 4) 8.4843 ( 5) 12.0000 ( 6) .1532 **** SORTED DEVIATIONS OF V(4) TEMPERATURE = 27.000 DEG С WORST CASE SUMMARY RUN MAXIMUM VALUE ALL DEVICES 8.6882 at T = 149.3200E-06 ( 103.99% of Nominal) NOMINAL 8.355 at T = 149.3200E-06 Рис. 17.31. Часть выходного файла для анализа на наихудший случай Цифровые схемы в CaptureВ Capture OrCAD имеется большой выбор цифровых устройств. Начнем новый проект с именем norgate и выберем Place, Part, перейдя к библиотеке eval. Начиная с компонентов 5550, 7400, 7401, …, вы увидите большой выбор цифровых компонентов, включая логические элементы И-НЕ, ИЛИ-НЕ, исключающее ИЛИ-инверторы, И-ИЛИ-инверторы, JK-триггеры, ведущие-ведомые триггеры, 2-разрядные двоичные полные сумматоры и другие. Все перечисленные устройства доступны в демонстрационной версии OrCAD. Схема ИЛИ-НЕВ последнем примере главы 9 мы рассматривали логическую схему 7400: 2-входовую схему ИЛИ-НЕ. В качестве источников V1 и V2 были использованы источники напряжения типа PWL с выходным напряжением в виде последовательностей импульсов, представляющих уровни логических нулей и единиц. Эта схема может быть введена и в Capture OrCAD, как показано на рис. 17.32. Чтобы создать V1 и V2, выберем компонент типа VPWL. Вспомним, как были описаны два источника в примере из главы 9: V1 1 0 PWL(0s 0V 0.1ms 1V 1s 1V 1.0001S 0V + 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V 4.0001s 1V 5s 1V) V2 2 0 PWL((0s 0V 1.5s 0V 1.50001s 1V 2.5s 1V 2.50001s 0V + 3.5s 0V 3.50001s 1V 3.70001s 0V 5s 0V)  Рис. 17.32. Схема для исследования логического элемента И-НЕ Войдя в Capture, дважды щелкните на компоненте V1 и в появившемся окне Property Editor введите следующие пары время-напряжение: «0s 0V 0.1ms 1V 1s 1V 1.0001s 0V 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V 4.0001s 1V». Отметим, что в Capture можно ввести только 10 пар время-напряжение, в то время как в PSpice их число не ограничено. Дважды щелкните на компоненте V2 и введите следующие пары время-напряжение: «0s 0V 1,5s 0V 1,50001s 1V 2,5s 1V 2,50001s 0V 3,5s 0V 3,50001s 1V 3,7s 1V 3,70001s 0V 5s 0V». Завершите схему, выбрав Place, Net Alias для узлов 1, 2 и Vout. Сохраните схему и подготовьте в PSpice новое моделирование с именем Norgate1. Выберите анализ переходных процессов на интервале t=5 мс с максимальным размером шага в 1 мс. Проведите анализ и получите в Probe графики V(1) и Vout, a V(2) — на отдельном графике, как показано на рис. 17.33. Курсор на рисунке показывает, что при t=1,2 с, когда и V(1) и V(2) равны логическому нулю, выход Vout равен логической единице. Уровни для обоих входных напряжений на этом графике совпадают с сеткой, что несколько затемняет картину.  Рис. 17.33. Диаграммы входных к выходного напряжений для элемента И-НЕ Небольшая часть выходного файла показана на рис. 17.34. Интереснее всего проследить, как входные напряжения задаются в соответствующих командах. В состав этой схемы входят как аналоговые, так и цифровые схемы, аналоговые источники VPWL подключены к логическому элементу И-НЕ 7402. Это заставляет программу PSpice создавать набор аналого-цифровых интерфейсов, что вносит в простой проект излишние осложнения. **** 09/06/99 14:20:30 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profiles Norgate1 *Libraries: * Local Libraries : * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .TRAN 0 5s 0 1ms .PROBE *Netlist File: .INC "norgate-SCHEMATIC1.net" *Alias File: **** INCLUDING norgate-SCHEMATIC1.net **** * source NORGATE V_V2 2 0 +PWL 0s 0V 1.5s 0V 1.50001s 1V 2.5s 1V 2.50001s 0V 3.5s 0V 3.50001s 1V 3.7s 1V + 3.70001s 0V 5s 0V V_V1 1 0 +PWL 0s 0V 0.1ms 1V 1s 1V 1.0001s 0V 2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V + 4.0001s 1V X_U1A 1 2 VOUT $G_DPWR $G_DGNV 7402 PARAMS: + IO_LEVEL=0 MNTYMXDLY=0 **** RESUMING norgate-SCHEMATIC1-Norgate1.sim.cir **** .INC "norgate-SCHEMATIC1.als" **** INCLUDING norgate-SCHEMATIC1.als **** .ALIASES V_V2 V2(+=2 -=0 ) V_V1 V1(+=1 -=0 ) X_U1A U1A(A=1 B=2 Y=VOUT VCC=$G_PWR GND=$G_DGND ) **** Generated AtoD and DtoA Interfaces **** Рис. 17.34. Выходной файл для логического элемента ИЛИ-НЕ Схема полусумматораНа самом деле нет необходимости использовать источник типа VPWL, чтобы обеспечить входные импульсы для цифровой схемы. Начните новый проект, использующий имя half. Библиотека Sourcestm содержит компонент DigStim1, условное обозначение которого показано на рис. 17.35, наряду с двумя другими компонентами из библиотеки eval: 2-входовой схемой исключающего ИЛИ 7486 и 2-входовой схемой И 7408. К выходу каждой из логических схем подключен короткий отрезок провода. Выходу компонента 7486, присвоен псевдоним «Sum», а выходу компонента 7408 — псевдоним «Carry».  Рис. 17.35. Схема полусумматора Выберите цифровую форму выходного напряжения под заголовком (А) с помощью Edit, PSpice Stimulus, New Stimulus, Digital, Clock, чтобы ввести цифровой таймер с именем Clock1. Установите параметры: частота 1 кГц, коэффициент заполнения 0,5, начальное значение 1 и нулевое запаздывание. Закройте редактор Stimulus и, модифицировав схему, сохраните изменения. Выберите теперь цифровую форму выходного напряжения под заголовком (В) с помощью Edit, PSpice Stimulus, New Stimulus, Digital, Clock, чтобы ввести цифровой таймер с именем Clock2. Он должен иметь параметры f=2 кГц, коэффициент заполнения 0,5, нулевое начальное значение и нулевое запаздывание. Редактор Stimulus отображает форму выходного сигнала для двух таймеров, как показано на рис. 17.36.  Рис. 17.36. Редактор Stimulus, показывает входные сигналы Clock1 и Clock2 Подготовьте моделирование на PSpice с именем Half1. Выполните анализ переходных процессов на интервале в 2 мс с максимальным размером шага в 2 мкс. Проведите анализ и получите в Probe графики сигналов А, В, Sum, Carry (рис. 17.37). Если использовать курсор, то уровни этих сигналов будут показаны как единицы или нули. Как показано на рисунке, при t=1,4 мс получаются значения: А=1, В=1, Sum=0 и Carry=1. Часть выходного файла показана на рис. 17.38. При таком формировании входных сигналов не возникает необходимости в создании интерфейсов перехода от аналоговых к цифровым сигналам и обратно, так как используются только цифровые сигналы. В перечне элементов через U обозначаются компоненты с цифровым выходом, а через X — подсхемы.  Рис. 17.37. Входные и выходные сигналы для полусумматора **** 10/18/99 21:28:59 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Half1 *Libraries: * Local Libraries : .STMLIB ".\HALF.stl" * From [PSPICE NETLIST] section of pspiceev.ini file: .lib "nom.lib" * Analysis directives: .TRAN 0 2ms 0 2us .PROBE *Netlist File: .INC "half-SCHEMATIC1.net" *Alias File: **** INCLUDING half-SCHEMATIC1.net **** * source HALF U_DSTM2 STIM(1,0) $G_DPWR $G_DGND В IO_STM STIMULUS=Clock2 U_DSTM1 STIM(1,0) $G_DPWR $G_DGND A IO_STM STIMULUS=Clock1 X_U2A А В SUM $G_DPWR $G_DGND 7486 PARAMS: + IO_LEVEL=0 MNTYMXDLY=0 X_U1A А В CARRY $G_DPWR $G_DGND 7408 PARAMS: + IO_LEVEL=0 MNTYMXDLY=0 **** RESUMING half-schematic1-half1.sim.cir **** .INC "half-SCHEMATIC1.als" **** INCLUDING half-SCHEMATIC1.als **** **** RESUMING half-schematicl-half1.sim.cir **** .END * E:\SPICE\HALF.stl written on Mon Sep 06 17:58:50 1999 * by Stimulus Editor — Evaluation Version 9.0 ;!Stimulus Get ;! Clock1 Digital Clock2 Digital ;!Ok ;!Plot Axis_Settings ;!Xrange 0s 4ms ;!AutoUniverse ;!XminRes 1ns ;!YminRes 1n ;!Ok .STIMULUS Clock1 STIM (1, 1) ;! CLOCK 1kHz 0.5 1 0 + +0s 1 + +500us 0 + Repeat Forever + +500us 1 + +500us 0 + EndRepeat .STIMULUS Clock2 STIM (1, 1) ;! CLOCK 2kHz 0.5 0 0 + +0s 0 + +250us 1 + Repeat Forever + +250us 0 + +250us 1 + EndRepeat .STIMULUS Clock2 STIM (1, 1) ;! CLOCK 2kHz 0.5 0 0 + +0s 0 + +250us 1 + Repeat Forever + +250us 0 + +250us 1 + EndRepeat Рис. 17.38. Выходной файл для полусумматора Схема для упрощения с использованием булевых функцийЦифровая схема, показанная на рис. 17.39, состоит из двух источников сигнала, одного элемента И-НЕ, и двух элементов ИЛИ-НЕ. Начните новый проект с именем mix и разместите компоненты, как показано на рисунке. В качестве учебного упражнения найдите таблицу истинности для схемы, затем на бумаге составьте булевые функции для схемы и упростите ее.  Рис. 17.39. Схема для упрощения с использованием булевых функций Источники сигналов для нашего проекта должны быть такими же, как в предыдущем примере, в котором использовались компоненты DigStiml из библиотеки sourcstm. Один из таймеров (DSTIM1) имеет частоту f=1 кГц, а другой (DSTM2) — f=2 кГц. Оба таймера в начале моделирования обнулены. Используйте Place, Net Alias, чтобы маркировать узлы А, В, С, D и Vout. Подготовьте моделирование с именем mix1. Вызовите анализ переходных процессов на интервале в 2 мс с максимальным шагом в 2 мкс. Проведите моделирование и получите в Probe все сигналы, как показано на рис. 17.40. Воспользуйтесь курсором, чтобы найти сигналы на выходах С, D, и Vout в различные моменты времени. Как следует из рисунка, при t=0,8 мс получаем А=1, В=1, С=0, D=0 и Vout=1. Убедитесь в соответствии этих результатов вашим таблицам истинности для каждой логической схемы. На рис. 17.41 показана часть выходного файла.  Рис. 17.40. Входные и выходные сигналы в схеме для упрощения **** 09/06/99 20:30:17 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Mix1 *Libraries: * Local Libraries : .STMLIB ".\MIX.stl" * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .TRAN 0 2ms 0 2us .PROBE *Netlist File: .INC "mix-SCHEMATIC1.net" *Alias File: **** INCLUDING mix-SCHEMATIC1.net **** * source MIX U_DSTM2 STIM(1,0) $G_DPWR $G_DGND В IO_STM STIMULUS=Clock2 U_DSTM1 STIM(1,0) $G_DPWR $G_DGND A IO_STM STIMULUS=Clock1 X_U3A С D VOUT $G_DPWR$G_DGND 7402 PARAMS: + IO_LEVEL=0 MNTYMXDLY=0 X_U2A А В D $G DPWR $G_DGND 7400 PARAMS: + IO_LEVEL=0 MNTYMXDLY=0 X_U1A ABC $G_DPWR $G_DGND 7402 PARAMS: + IO_LEVEL=0 MNTYMXDLY=0 **** RESUMING mix-SCHEMATIC1-Mix1.sim.cir **** .INC "mix-SСHEMATIC1.als" **** INCLUDING mix-SCHEMATICl.als **** .ALIASES .END * E:\SPICE\MIX.stl written on Mon Sep 06 20:26:10 1999 * by Stimulus Editor — Evaluation Version 9.0 ;!Stimulus Get ;! Clock1 Digital Clock2 Digital ;!Ok ;!Plot Axis_Settings ;!Xrange 0s 4ms ;!AutoUniverse ;!XminRes 1ns ;!YminRes 1n ;!Ok .STIMULUS Clock1 STIM (1, 1) ;! CLOCK 1kHz 0.5 0 0 + +0s 0 + +500us 1 + Repeat Forever + +500us 0 + +500us 1 + EndRepeat .STIMULUS Clock2 STIM (1, 1) ;! CLOCK 2kHz 0.5 0 0 + +0s 0 + +250us 1 + Repeat Forever + +250us 0 + +250us 1 + EndRepeat .STIMULUS Clock2 STIM(1, 1) ;! CLOCK 2kHz 0.5 0 0 + +0s 0 + +250us 1 + Repeat Forever + +250us 0 + +250us 1 + EndRepeat Рис. 17.41. Выходной файл схемы для упрощения D-триггерЧтобы показать работу D-триггера, начните новый проект с именем dflip. Введите схему, показанную на рис. 17.42, применив в качестве D-триггера компонент 7474 из библиотеки eval. Это — запускаемый положительным фронтом D-триггер с предварительной установкой и сбросом. Используйте компонент DigStim1 из библиотеки sourcstm для создания сигналов PS, D и CL и компонент DigClock из библиотеки исходных модулей для таймера. Установите для сигнала PS параметры: частота f=1 кГц, коэффициент заполнения 0,5, начальное значение 1 и запаздывание 0. Соответствующие значения для сигнала D будут: 1 кГц; 0,5, 1 и 0,75 мс, а для CL они равны 0,8 кГц; 0,5, 0 и 0 мс соответственно. Формы сигналов для цифровых таймеров показаны на рис. 17.43. Параметры настройки DigClock: задержка 0, время включенного состояния 0,4 мс, время выключенного состояния 0,6 мс, начальное значение 0.  Рис. 17.42. Схема для исследования D-триггера  Рис. 17.43. Временные диаграммы для различных источников сигналов в Stimulus Editor Подготовьте анализ переходных процессов с именем Dflip1 на временном интервале в 2 мс с максимальным шагом в 2 мкс. Проведите моделирование и получите в Probe графики всех возможных сигналов. Сравните ваши результаты с показанными на рис. 17.44. Проверьте результаты, основываясь на ваших знаниях о работе триггера. Почему присутствуют временные периоды, когда сигналы Q и Qbar не являются дополнительными? На рис. 17.45 показана часть выходного файла, где вы можете видеть временные параметры для различных источников сигналов.  Рис. 17.44. Временные диаграммы сигналов в схеме на рис. 17.42 **** 09/06/99 21:05:11 *********** Evaluation PSpice (Nov 1998) ************** ** circuit file for profile: Dflip1 *Libraries: * Local Libraries : .STMLIB ".\DFLIP.stl" * From [PSPICE NETLIST] section of pspiceev.ini file: .lib nom.lib *Analysis directives: .TRAN 0 2ms 0 2us .PROBE *Netlist File: .INC "dflip-SCHEMATIC1.net" *Alias File: **** INCLUDING dflip-SCHEMATIC1.net **** * source DFLIP U_DSTM3 STIM(1,0) $G_DPWR $G_DGND N00046 IO_STM STIMULUS_CL U_DSTM2 STIM(1,0) $G_DPWR $G_DGND N00022 IO_STM STIMULUS=D U_DSTM1 STIM(1,0) $G_DPWR $G_DGND N00015 IO_STM STIMULUS=PS X_U1A N00046 N00022 N00034 N00015 M_UN0001 M_UN0002 $G_DPWR $G_DGND + 7474 PARAMS: + IO_LEVEL=0 MNTYMXDLY=0 U_DSTM4 STIM(1,1) $G_DPWR $G_DGND N00034 IO_STM IO_LEVEL=0 + 0 0 + +0 1 + REPEAT FOREVER + +0.4ms 0 + +0.6ms 1 + ENDREPEAT .STIMULUS PS STIM (1, 1) ;! CLOCK 1kHz 0.5 1 0 + +0s 1 + +500us 0 + Repeat Forever + +500us 1 + +500us 0 + EndRepeat .STIMULUS D STIM (1, 1) ;! CLOCK 1kHz 0.5 1 0.75ms + +0s 1 + +750us 0 + Repeat Forever + +500us 1 + +500us 0 + EndRepeat .STIMULUS CL STIM (1, 1) ;! CLOCK 0.8kHz 0.5 0 0 + +0s 0 + +625us 1 + Repeat Forever + +625us 0 + +625us 1 + EndRepeat .STIMULUS CL STIM (1, 1) ;! CLOCK 0.8kHz 0.5 0 0 + +0s 0 + +625us 1 + Repeat Forever + +625us 0 + +625us 1 + EndRepeat .STIMULUS D STIM (1, 1) ;! CLOCK 1kHz 0.5 1 0.75ms + +0s 1 + +750us 0 + Repeat Forever + +500us 1 + +500us 0 + EndRepeat Рис. 17.45. Выходной файл для D-триггера |

|

||

|

Главная | В избранное | Наш E-MAIL | Добавить материал | Нашёл ошибку | Наверх |

||||

|

|

||||